- 您现在的位置:买卖IC网 > Sheet目录1905 > ATMEGA649V-8MI (Atmel)IC AVR MCU FLASH 64K 1.8V 64QFN

70

2552K–AVR–04/11

ATmega329/3290/649/6490

SS/PCINT8 – Port B, Bit 0

SS: Slave Port Select input. When the SPI is enabled as a Slave, this pin is configured as an

input regardless of the setting of DDB0. As a Slave, the SPI is activated when this pin is driven

low. When the SPI is enabled as a Master, the data direction of this pin is controlled by DDB0.

When the pin is forced to be an input, the pull-up can still be controlled by the PORTB0 bit

PCINT8, Pin Change Interrupt Source 8: The PB0 pin can serve as an external interrupt source.

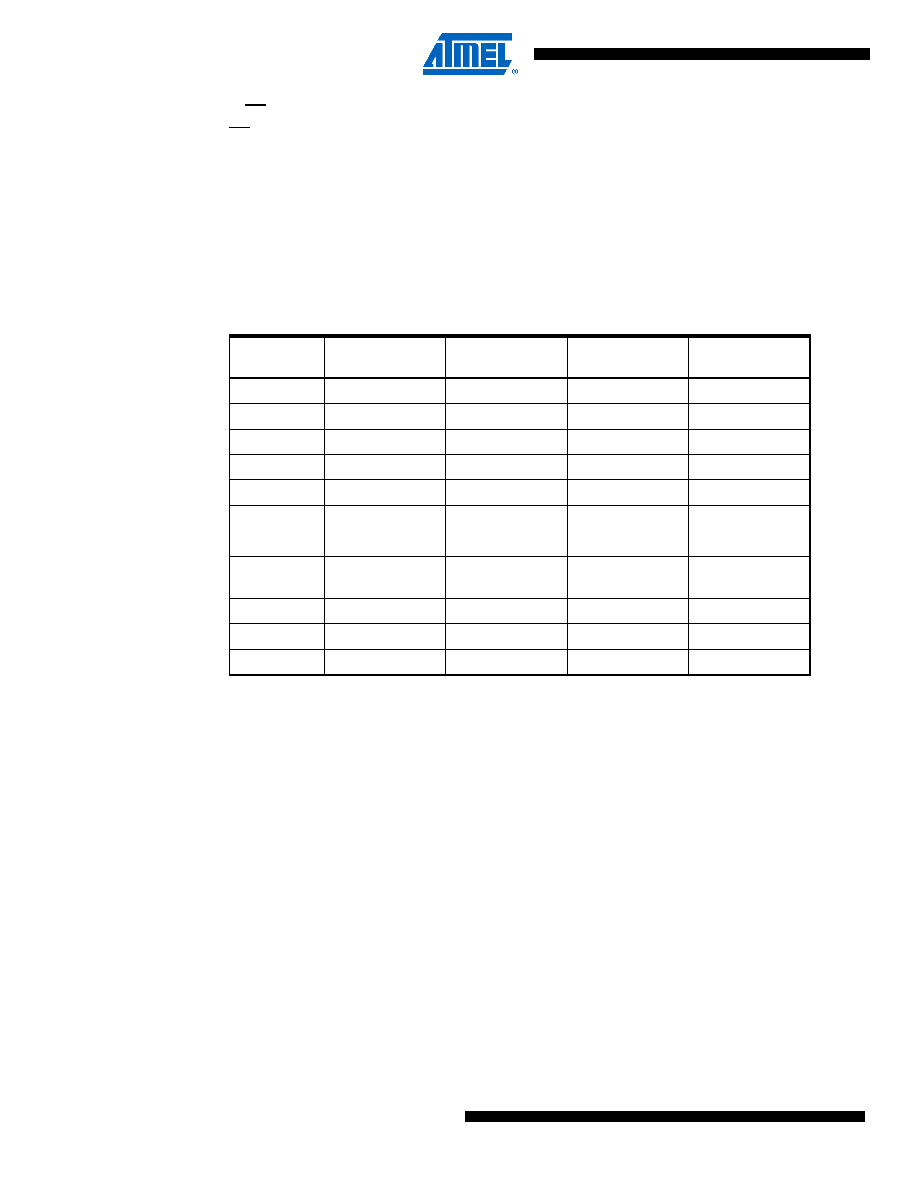

Table 13-7 and Table 13-8 relate the alternate functions of Port B to the overriding signals

shown in Figure 13-5 on page 65. SPI MSTR INPUT and SPI SLAVE OUTPUT constitute the

MISO signal, while MOSI is divided into SPI MSTR OUTPUT and SPI SLAVE INPUT.

Table 13-7.

Overriding Signals for Alternate Functions in PB7:PB4

Signal

Name

PB7/OC2A/

PCINT15

PB6/OC1B/

PCINT14

PB5/OC1A/

PCINT13

PB4/OC0A/

PCINT12

PUOE

000

0

PUOV

000

0

DDOE

0

DDOV

0

PVOE

OC2A ENABLE

OC1B ENABLE

OC1A ENABLE

OC0A ENABLE

PVOV

OC2A

OC1B

OC1A

OC0A

PTOE

–––

–

DIEOE

PCINT15

PCIE1

PCINT14

PCIE1

PCINT13

PCIE1

PCINT12

PCIE1

DIEOV

111

1

DI

PCINT15 INPUT

PCINT14 INPUT

PCINT13 INPUT

PCINT12 INPUT

AIO

–––

–

发布紧急采购,3分钟左右您将得到回复。

相关PDF资料

ATMEGA8515L-8JUR

MCU AVR 8KB FLASH 8MHZ 44PLCC

ATMEGA8515L-8PJ

IC MCU AVR 8K 5V 8MHZ 40-DIP

ATMEGA8535-16JUR

MCU AVR 8K FLASH 16MHZ 44PLCC

ATMEGA8535L-8PJ

IC MCU AVR 8K 5V 8MHZ 40-DIP

ATMEGA88-15MT2

MCU AVR 8K FLASH 15MHZ 32-QFN

ATMEGA88-20AUR

MCU AVR 8K FLASH 20MHZ 32TQFP

ATMEGA88P-20AUR

MCU AVR 8KB FLASH 20MHZ 32TQFP

ATMEGA8HVA-4CKU

MCU AVR 8K FLASH 4MHZ 36-LGA

相关代理商/技术参数

ATmega649V-8MU

功能描述:8位微控制器 -MCU AVR 64K FLASH 2K EE 4K SRAM ADC LCD RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

ATMEGA649V-8MUR

功能描述:8位微控制器 -MCU AVR 64KB FLSH 2KB EE 4KB SRAM LCD8MHz1.8V RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

ATMEGA64A-AN

功能描述:8位微控制器 -MCU 16MHz 105C RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

ATMEGA64A-ANR

功能描述:8位微控制器 -MCU 16MHz 105C RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

ATMEGA64A-AU

功能描述:8位微控制器 -MCU 64K Flsh 2K EEPROM 4K SRAM 16MHz RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

ATMEGA64A-AUR

功能描述:8位微控制器 -MCU AVR 64KB FLSH 2KB EE 4KB SRAM-16MHz IND RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

ATMEGA64A-MN

功能描述:8位微控制器 -MCU 16MHz MLF 105C RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

ATMEGA64A-MNR

功能描述:8位微控制器 -MCU 16MHz MLF105C RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT